在互补金属氧化物半导体(CMOS)之上构建微机电系统(MEMS)需要低热条件、电活性且厚的多晶硅薄膜。然而,形成这些多晶硅薄膜在该领域是一项挑战。自然杂志旗下微系统与纳米工程期刊(Microsystems & Nanoengineering)于2024年发表了一篇文章《Low-Thermal-Budget Electrically Active Thick Polysilicon for CMOS-First MEMS-Last Integration》提出了使用电子束蒸发(UHVEE)在超高真空条件下沉积的原位掺磷硅薄膜的开发。

这篇文章深入研究了在CMOS电路上方构建MEMS器件时,如何在低热预算的条件下制造出具有良好电气和机械性能的厚多晶硅薄膜。研究团队开发了一种使用超高真空电子束蒸发(UHVEE)技术沉积的掺磷多晶硅薄膜,这种薄膜具有高结晶度、低内应力和良好的导电性。通过实验验证,这种薄膜适合在低于500°C的温度下制造MEMS器件,如梳状驱动结构。研究表明,该技术可以实现CMOS-First MEMS-Last集成方案,为低成本、高性能的CMOS-MEMS单片集成提供了新的可能性。

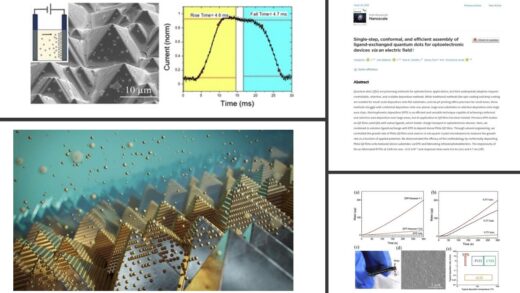

该工艺产生了电活性、完全结晶、低应力、光滑且厚的多晶硅薄膜,同时具有低热的条件。研究了磷掺杂UHVEE多晶硅薄膜的晶体学、机械和电学性能,并将其与本征硅和硼掺杂的UHVEE硅薄膜进行了比较。使用拉曼光谱、X射线衍射(XRD)、透射电子显微镜(TEM)和原子力显微镜(AFM)进行晶体学和表面形貌研究。使用晶圆弯曲、悬臂梁偏转轮廓和共振频率测量来研究样品的机械性能。此外,还进行了电阻率测量以研究薄膜的电学性能。开发了高垂直、高纵横比的UHVEE多晶硅微加工技术。在温度低于500°C的条件下,设计、模拟、制造并表征了一种由20μm厚原位掺磷UHVEE薄膜制成的梳状驱动结构,用作执行器和惯性传感器。结果首次证明了UHVEE多晶硅独特地使低热预算的机械和电气功能MEMS设备的实现成为可能。

由于其优异的机械和电气性能,硅显然是用于形成微机电系统(MEMS)中机械和电气设备的主导材料。硅不表现出机械滞后效应。通过选择性掺杂n型和p型杂质,可以轻松且精确地控制该材料的电学性能。此外,硅是一种相对廉价的材料,适合批量制造。该材料在集成电路技术领域至关重要,尤其是在CMOS的发展中,使CMOS-MEMS单片集成成为实现相对小型和高功能系统的必要条件。已经提出并研究了各种CMOS-MEMS单片集成方法。根据MEMS工艺与CMOS工艺的集成阶段,现有的单片集成被分类为MEMS-First、MEMS-Intermediate或MEMS-Last方法。MEMS-Last方法具有模块化集成的优点。在这个过程中,CMOS和MEMS可以在独立的晶圆厂中开发,并在CMOS之上构建MEMS。因此,MEMS-Last集成的关键要求是尽量减少实现MEMS组件所需的热预算。最小化热预算可以防止CMOS电路损坏并保持系统完整性。

晶体学特性:拉曼光谱、XRD和TEM的结果表明,掺磷UHVEE多晶硅薄膜具有良好的晶体结构和结晶度。拉曼光谱显示出清晰的Si-Si振动峰,表明薄膜具有高结晶度。XRD分析显示,薄膜的晶粒尺寸较大,并且具有良好的晶体取向。TEM图像进一步确认了这一点。

机械性能:机械测试结果显示,掺磷UHVEE薄膜具有低内应力和高杨氏模量。这些特性使其适合用于需要高机械强度和稳定性的MEMS应用。悬臂梁偏转轮廓测量表明,薄膜的内应力非常低,这对于避免器件变形非常重要。

电学性能:电阻率测量结果表明,掺磷UHVEE薄膜的电阻率较低,表明其具有良好的导电性。这种导电性使得该薄膜适合作为电活性材料,尤其是在需要低热预算的CMOS-MEMS集成应用中。

MEMS器件的性能:制造的梳状驱动结构展示了优异的机械和电学性能。实验结果显示,使用掺磷UHVEE薄膜制造的MEMS器件在低温(<500°C)下具有稳定的性能,这验证了该薄膜在低热预算CMOS-MEMS集成中的潜力。

使用UHVEE技术沉积的掺磷多晶硅薄膜表现出优异的晶体学、机械和电学性能,特别适合用于制造机械和电气功能的MEMS器件。这一成果首次证明了在低热预算条件下实现具有优良机械和电气性能的MEMS器件是可能的,为CMOS-MEMS单片集成的实现提供了新的途径。