戈登·摩尔 (Gordon Moore) 在1965 年和 1975 年发表的著名论文指导了 50 多年的半导体电子学发展。然而,场效应晶体管(Field Effect Transistor, FET)正在接近进一步小型化的物理极限,相关成本的上升和投资回报率的下降似乎正在减缓发展的步伐。这种渐进式的“摩尔定律终结”绝非标志着进步的终结,随着研究和开发的重点从技术小型化转向新设备、新集成技术以及新计算架构,信息技术将开启的新纪元。

By making things smaller, everything gets better simultaneously. There is little need for tradeoffs. The speed of our products goes up, the power consumption goes down, system reliability, as we put more of the system on a chip, improves by leaps and bounds, but especially the cost of doing thing electronically drops as a result of the technology.

Lithography and the future of Moore’s Law published by Gordon Moore on 2006 IEEE Solid-State Circuits Society Newsletter

由于光刻技术的不断进步,所生产产品的复杂性不断增加,在相当大的程度上实现越来越高的密度,半导体技术取得了长足的进步。摩尔在2006年的电气电子工程协会固态电路学会通讯杂志(IEEE Solid-State Circuits Society Newsletter)发表了署名文章Lithography and the future of Moore’s Law再一次回顾了举世瞩目的摩尔定律(电路复杂度每两年翻一番),但所有指数趋势都将迎来终结。

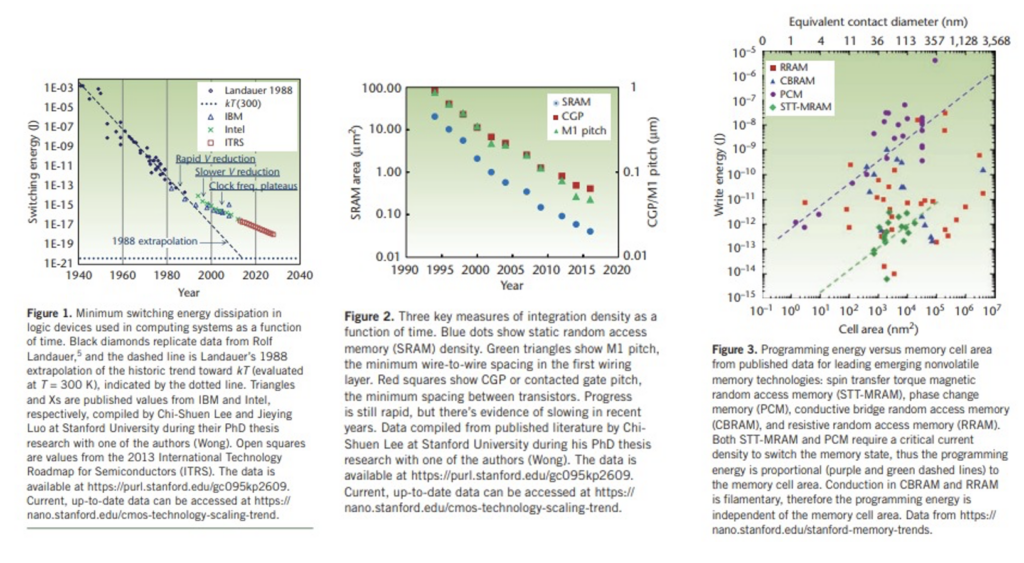

2017年哥伦比亚大学教授Thomas N. Theis和斯坦福大学教授 H.-S. Philip Wong联名在电气电子工程协会科学与工程计算杂志(IEEE Computing in Science & Engineering)发表了一篇对学术界和工业界影响深远的文章The End of Moore’s Law: A New Beginning for Information Technology系统的讨论了摩尔定律即将终结的原因并对未来的半导体电子技术做了展望。

两位教授提出栅极绝缘体(Gate Insulator)厚度和工作电压不能再与其他器件尺寸一起简单地减小。绝缘体厚度的进一步减小将导致通过直接量子隧穿(Direct Quantum Tunneling)的栅极漏电流(Gate Leakage Current)呈指数的增加。工作电压摆幅的进一步降低会导致“开”状态下通道电流低到无法承受(开关速度也会降低到无法承受),“关”状态下的漏电流增加(无源功率也会增加到无法承受)。电压的进一步降低众所周知有悖于物理学原理。摩尔定律的终点似乎就在不远的未来。

基于新设备、新集成工艺和新计算架构的原创技术或将推动并引领半导体行业的发展。新设备指的是与场效应晶体管(FET)工作原理不同的不受其基本限制(特别是电压缩放限制)的设备。新集成技术指的是单片集成(Monolithic Integration)在三个维度上以细粒度的方式(Fine-grained Manner)实现整体集成并将内存浸入(Immerse)计算单元中。新架构指的是比冯诺依曼架构(Von Neumann Architecture)更节能更高级别的架构。